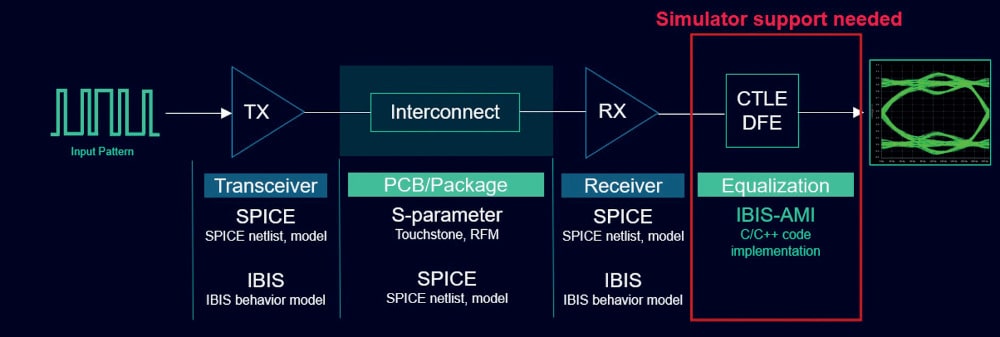

High-speed signals enable electronic systems by using memory interfaces, SerDes channels, data center backplanes and connectivity in automobiles. Challenges arise from signal distortions like inter-symbol interference, channel loss and dispersion effects. Multi-gigabit data transfer rates in High-Bandwidth Memory (HBM) and Double Data Rate (DDR) require equalization techniques like Continuous Time Linear Equalization (CTLE) and Decision Feedback Equalization (DFE) to ensure adequate eye openings.

Verifying high-speed links calls for SPICE accuracy using IBIS and IBIS-AMI models. For chip-level and block-level circuits you still need SPICE models. Siemens has developed a tool that simulates IBIS, IBIS-AMI, S-parameter interconnect and SPICE together, enabling high-speed link v…

High-speed signals enable electronic systems by using memory interfaces, SerDes channels, data center backplanes and connectivity in automobiles. Challenges arise from signal distortions like inter-symbol interference, channel loss and dispersion effects. Multi-gigabit data transfer rates in High-Bandwidth Memory (HBM) and Double Data Rate (DDR) require equalization techniques like Continuous Time Linear Equalization (CTLE) and Decision Feedback Equalization (DFE) to ensure adequate eye openings.

Verifying high-speed links calls for SPICE accuracy using IBIS and IBIS-AMI models. For chip-level and block-level circuits you still need SPICE models. Siemens has developed a tool that simulates IBIS, IBIS-AMI, S-parameter interconnect and SPICE together, enabling high-speed link verification.

IBIS-AMI

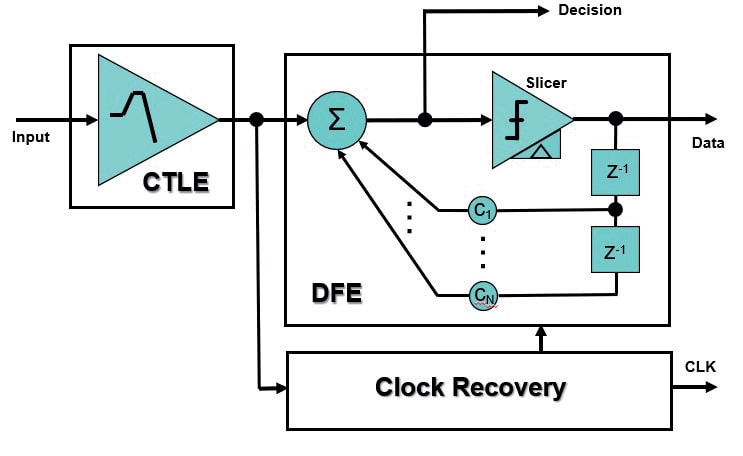

With IBIS-AMI you can now simulate the equalization effects, CTLE and DFE for high-speed channel simulations.

The Rx IBIS-AMI data-flow model has algorithmic descriptions for each function: CTLE, DFE, Clock Recovery.

In the past you could simulate a SPICE netlist, S-parameter files and IBIS models with one simulator, then another separate tool for IBIS-AMI, creating multiple iterations. Now, it’s possible verify these circuits using Solido SPICE, reducing both iterations and verification times.

Solido Simulation Suite

Last year Siemens announced Solido Simulation Suite:

- Solido SPICE

- Solido LibSPICE

- Solido FastSPICE

The Solido SPICE simulator supports IBIS-AMI models, IBIS, S-parameters, lossy coupled transmission line models and DSPF used for high-speed signaling projects. Verification using Solido SPICE shows nonlinear effects in AMI equalized eye openings in the presence of channel, I/O buffer, and power delivery.

DDR5

With Solido SPICE it’s possible to verify Chip-to-Chip (C2C) and Chip-to-Module (C2M) designs, where the chip is at SPICE-level, and the Rx receive-side chip has IBIS and IBIS-AMI models. For a DDR5 application the C2C verification of Read and Write cycles use either Tx or Rx modeled with IBIS and IBIS-AMI. Digital equalization is modeled with IBIS-AMI, then Solido SPICE simulates the mix of SPICE-level and all models.

SerDes

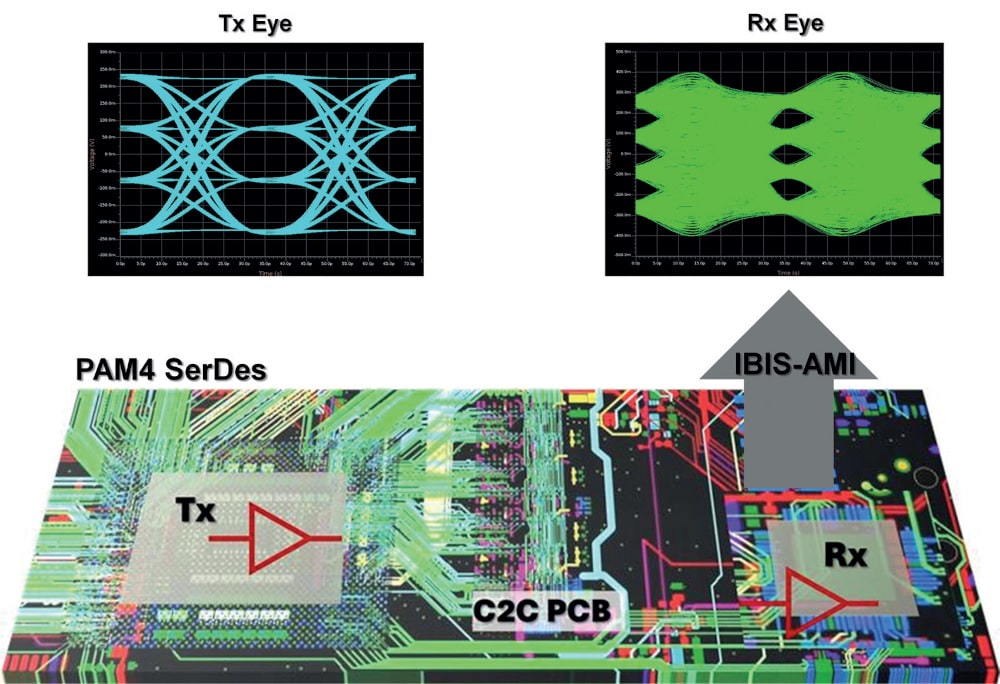

Shown below is the Rx eye diagram for an AMI processed output waveform on a 28Gbaud PAM4 C2C interface. The Tx is modeled at SPICE-level, PCB interconnects are included, dielectric losses and edge connector are modeled, and the receive-side Rx uses IBIS-AMI for the CTLE and DFE equalization.

NRZ and PAM4

Clock and Data Recovery (CDR) functions can be modeled with IBIS-AMI to support both Non-Return-to-Zero (NRZ) and Pulse Amplitude Modulation (PAM4) encoding. Solido SPICE enables SPICE-level verification of both high-speed DDR5 and SerDes chip designs using models for IBIS and IBIS-AMI, so that chips from other manufacturers can be simulated in your electronic system.

HyperLynx SI

With the HyperLynx SI tool a system designer can do signal integrity analysis at the system and board-level, all without having to be an SI expert. Users of Solido SPICE are getting shared IBIS-AMI technology from HyperLynx, ensuring consistent analysis results when alternating between circuit and system-level tools.

Summary

High-speed signaling requires an accurate verification approach. SPICE simulation is capable to capture non-linear effects down to the transistor-level. Therefore, supporting IBIS-AMI with SPICE to capture non-linear effects is crucial to such applications including SerDes, HBM and other applications with PAM4. Solido SPICE is able to verify these complex systems accurately and quickly.

Read the entire 10 page White Paper from Siemens online, Combining SPICE with IBIS-AMI: Solving advanced signal integrity verification challenges with Solido SPICE.

Related Blogs

- Cracking post-route Compliance Checking for High-Speed Serial Links with HyperLynx

- Will my High-Speed Serial Link Work?

- Standardization of Chiplet Models for Heterogeneous Integration

- DDR5 Design Approach with Clocked Receivers

- Next Generation of Systems Design at Siemens

- Three New Circuit Simulators from Siemens EDA

Share this post via: